AI Becomes Infrastructure: From Coding Agents to Edge, Quantum, Biotech

Published Jan 4, 2026

If you still think AI is just autocomplete, wake up: in the two weeks from 2024-12-22 to 2025-01-04 major vendors moved AI into IDEs, repos, devices, labs and security frameworks. You’ll get what changed and what to do. JetBrains (release notes 2024-12-23) added multifile navigation, test generation and refactoring inside IntelliJ; GitHub rolled out Copilot Workspace and IDE integrations; Google and Microsoft refreshed enterprise integration patterns. Qualcomm and Nvidia updated on-device stacks (around 2024-12-22–12-23); Meta and community forks pushed sub‐3B LLaMA variants for edge use. Quantinuum reported 8 logical qubits (late 2024). DeepMind/Isomorphic and open-source projects packaged AlphaFold 3 into lab pipelines. CISA and OSS communities extended SBOM and supply‐chain guidance to models. Bottom line: AI’s now infrastructure—prioritize repo/CI/policy integration, model provenance, and end‐to‐end workflows if you want production value.

From Qubits to Services: Error Correction Is the Real Quantum Breakthrough

Published Dec 6, 2025

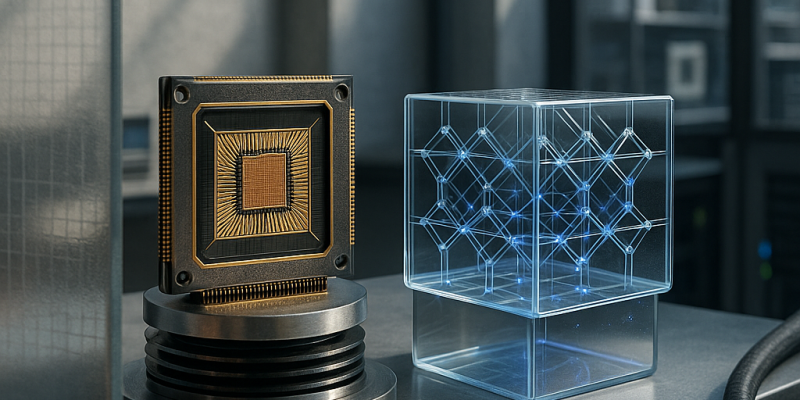

If you’re still judging progress by raw qubit headlines, you’re missing the real shift: in the last two weeks several leading programs delivered concrete advances in error correction and algorithmic fault tolerance. This short brief tells you what changed, why it matters for customers and revenue, and what to do next. What happened: hardware teams reported increased physical qubit counts (dozens to hundreds) with better coherence, experiments that go beyond toy codes, and tighter classical‐control/decoder integration—yielding small logical qubit systems where logical error rates sit below physical rates. Why it matters: AI, quant trading, biotech and software teams will see quantum capabilities emerge as composable services—hybrid quantum‐classical kernels for optimization, Monte Carlo, and molecular simulation—if logical qubit roadmaps mature. Risks: large overheads (hundreds–thousands of physical per logical) and timeline uncertainty. Immediate steps: get algorithm‐ready, design quantum‐aware integrations, and track logical‐qubit and fault‐tolerance milestones.

Quantum Leap: Fault-Tolerant Hardware Moves from Lab to Reality

Published Nov 22, 2025

Worried quantum is shifting from lab hype to real business risk and opportunity? Read this and you’ll know what changed, when, who’s involved, key numbers, and the near‐term outlook. In November 2025 IQM unveiled Halocene (Nov 13) — an on‐prem QEC platform with 150 physical qubits and a 99.7% two‐qubit fidelity target, slated commercial by end‐2026; IBM revealed Nighthawk (Nov 2025) with 120 qubits, 218 tunable couplers, a move to 300 mm wafers to double R&D speed and 10× chip complexity, plus qLDPC decoding in <480 ns; Quantinuum launched Helios (Nov 5–6) — 98 fully connected qubits, 99.9975% single‐qubit fidelity, 48 logical qubits at 2:1 encoding and NVIDIA GB200 integration for 2026 deployment in Singapore; Microsoft committed DKK 1bn to topological qubit manufacturing in Lyngby. Impact: faster path to fault‐tolerant quantum for AI, finance, biotech, security and infrastructure. Near term: commercial systems and regional deployments in 2026; watch gate fidelity, logical‐qubit ratios and sub‐microsecond decoding.

Helios and IBM Roadmaps Make Fault-Tolerant Quantum Imminent

Published Nov 18, 2025

Think quantum advantage is still vaporware? This week’s hardware pushes say otherwise—and here’s what you need in 60 seconds: on 2025-11-06 Quantinuum launched Helios: 98 barium‐ion physical qubits delivering 48 error‐corrected logical qubits with single‐qubit fidelity 99.9975% and two‐qubit 99.921%, plus DARPA picked Quantinuum for Stage B of the Quantum Benchmarking Initiative to validate its Lumos-to‐2033 roadmap. On 2025-11-12 IBM unveiled Loon (a pathfinder for error‐correction architectures) and announced Nighthawk for end‐2025, which it says could beat classical machines on select tasks by late 2026 and aims for useful systems by 2029. Why it matters: error correction is moving from theory into hardware, changing timelines for customers, investors, and security. Watch Helios’ real workloads, DARPA’s evaluation, Nighthawk benchmarks and Loon’s architecture next.

Quantum Error Correction Advances Push Fault-Tolerant Computing Toward Reality

Published Nov 16, 2025

Between 2025-11-02 and 2025-11-12 the quantum computing field reported multiple QEC advances: DARPA selected QuEra and IBM for Stage B of its Quantum Benchmarking Initiative on 2025-11-06, awarding up to US$15 million over 12 months each to validate paths toward fault-tolerant systems with QBI targeting “computational value exceeds cost” by 2033; Princeton on 2025-11-05 demonstrated a tantalum-on-silicon superconducting qubit with coherence >1 ms (≈3× prior lab best, ≈15× industry standard); ECCentric published on 2025-11-02 benchmarking code families and finding connectivity more important than code distance; BTQ/Macquarie published an LDPC/shared-cavity QEC method; IBM revealed its Loon chip on 2025-11-12 and expects Nighthawk by end-2025 with possible task-level quantum advantage by late-2026. These developments lower error-correction overhead, emphasize hardware–code co-design, and point to near-term validation steps: QBI Stage C, public Loon/Nighthawk metrics, and verification of logical-qubit lifetimes.

IBM’s Loon Chip Signals Rapid Path to Fault-Tolerant Quantum Computing

Published Nov 16, 2025

On 12 November 2025 IBM announced the experimental Loon chip, which uses a cellular‐systems‐derived error‐correction approach and aims to help deliver useful quantum computers by 2029; alongside it IBM unveiled Nighthawk, slated for external research access by end‐2025 and expected to outperform classical computers on some tasks by late‐2026. About a week earlier IBM showed a quantum error‐correction algorithm running on AMD FPGAs at speeds 10× faster than demanded by performance needs. These developments matter because Loon’s design and FPGA integration could lower logical error rates and reduce the physical‐qubit overhead, accelerating timelines and pressing software, algorithm and infrastructure readiness. Immediate milestones to watch are Nighthawk public benchmarks in late‐2025 and external quantum‐advantage demonstrations by late‐2026.

1 ms Superconducting Qubit: Princeton's Tantalum Breakthrough Accelerates Fault-Tolerant Quantum Computing

Published Nov 16, 2025

On November 5, 2025, a Princeton University team led by Andrew Houck, Nathalie de Leon and Robert Cava reported in Nature a superconducting qubit made from tantalum on high‐purity silicon with coherence exceeding 1 ms—about three times longer than prior lab best (0.3–0.4 ms) and roughly 15× higher than many current processors. Longer coherence reduces error‐correction overhead and allows more operations before errors, improving prospects for fault tolerance; related devices showed T1 up to 1.68 ms, Q ≈ 1.5×10^7 (peaks 2.5×10^7) and single‐qubit fidelities of 99.994% (MIT reported 99.998%). Princeton projects that integrating this design into processors like Willow could yield ~1,000× performance gains. Immediate outlook: raise two‐qubit fidelities (target >99.9%), demonstrate logical‐qubit break‐even in 2026, and standardize tantalum‐on‐silicon fabrication in early 2026.

Verifiable Quantum Advantage: Google's Willow and IBM's FPGA Error-Correction Breakthrough

Published Nov 12, 2025

On 2025-10-22 Google and IBM announced complementary quantum milestones that move the field toward practical use: Google’s 105-qubit Willow processor ran the new Quantum Echoes OTOC algorithm, producing verifiable expectation values (including NMR-inferred geometries for 15- and 28-atom molecules) and executing 13,000× faster than the best classical algorithm, while Willow reported single-qubit fidelity ~99.97%, entangling gates ~99.88% and readout ~99.5%; IBM demonstrated a quantum error‐correction routine running in real time on conventional AMD FPGAs at 10× the required speed, advancing its Starling roadmap toward 2029. These results matter because verifiability and faster, FPGA-enabled error correction make real applications (molecular modeling, materials, drug discovery) more plausible; next steps are scaling to logical qubits, external replication of Quantum Echoes and error‐correction results, and broader industry benchmarks, with Google projecting useful applications within five years.

Princeton’s Tantalum-Silicon Qubit Surpasses 1 ms, Propelling Practical Quantum Computing

Published Nov 12, 2025

On 2025-11-05 Princeton researchers reported a superconducting transmon qubit with coherence times exceeding 1 millisecond—three times prior lab records and nearly 15× the industry standard for large-scale processors—achieved by replacing aluminum-on-sapphire with tantalum circuits on high-quality silicon. The advance could make processors like Google’s Willow roughly 1,000× more reliable, directly improving error‐correction performance and amplifying benefits in larger systems; the design is compatible with transmon architectures used by major vendors. Key numbers: >1 ms coherence, 3× lab improvement, ~15× industry gap, and the 2025-11-05 announcement date. Remaining gaps include scaling coherence across arrays, integrating control/readout/error‐correction while preserving coherence, and ensuring fabrication yield and reproducibility. Immediate outlook: research labs will likely adopt tantalum‐silicon testbeds, industry may revise roadmaps, and funding/policy could shift toward materials and fabrication efforts.